FPGA-Based RF Signal Processing: Exploring the Red Pitaya STEMlab 125-14

-

Posted by

Red Pitaya Technical Editorial Team

, March 17, 2026

Red Pitaya Technical Editorial Team

, March 17, 2026

In the world of FPGA and SoC development, tools like Vivado and PetaLinux are industry standards. However, as designs move closer to complex algorithmic modeling, the bridge between Simulink and Programmable Logic becomes vital.

In a recent deep-dive by the MicroZed Chronicles, the focus shifts to a powerful tool for this bridge: Vitis Model Composer, and how it integrates with the hardware capabilities of the Red Pitaya STEMlab 125-14.

The Hybrid Workflow: Vitis Model Composer & Simulink

Traditionally, algorithm developers stay in MATLAB/Simulink, while HDL engineers work in Vivado. Vitis Model Composer breaks this barrier by providing HDL and HLS blocks directly within Simulink.

This environment is particularly effective for signal processing tasks such as:

- AM Modulation/Demodulation: Using Model Composer to visualize real-time FFTs of demodulated signals.

- Rapid Prototyping: Moving from a mathematical model to a hardware-ready bitstream without writing manual RTL.

Hardware Spotlight: Red Pitaya STEMlab 125-14

To test these high-speed algorithms, you need hardware that offers more than just a standard development board. The Red Pitaya (Gen 2) serves as a capable mixed-signal platform with the following core specs:

| Component | Specification |

| SoC | Zynq 7010 / 7020 |

| ADC | Dual 14-bit, 125 MSPS (LTC2145-14) |

| DAC | Dual 14-bit, 125 MSPS (AD9767) |

| Expansion | 16 Digital I/O + 4 Analog inputs/outputs |

Unlike generic FPGA boards, the Red Pitaya includes a full software stack that allows it to function as a standalone instrument (Oscilloscope, Spectrum Analyzer) or be controlled remotely via Python or MATLAB.

Analyzing Analog Performance

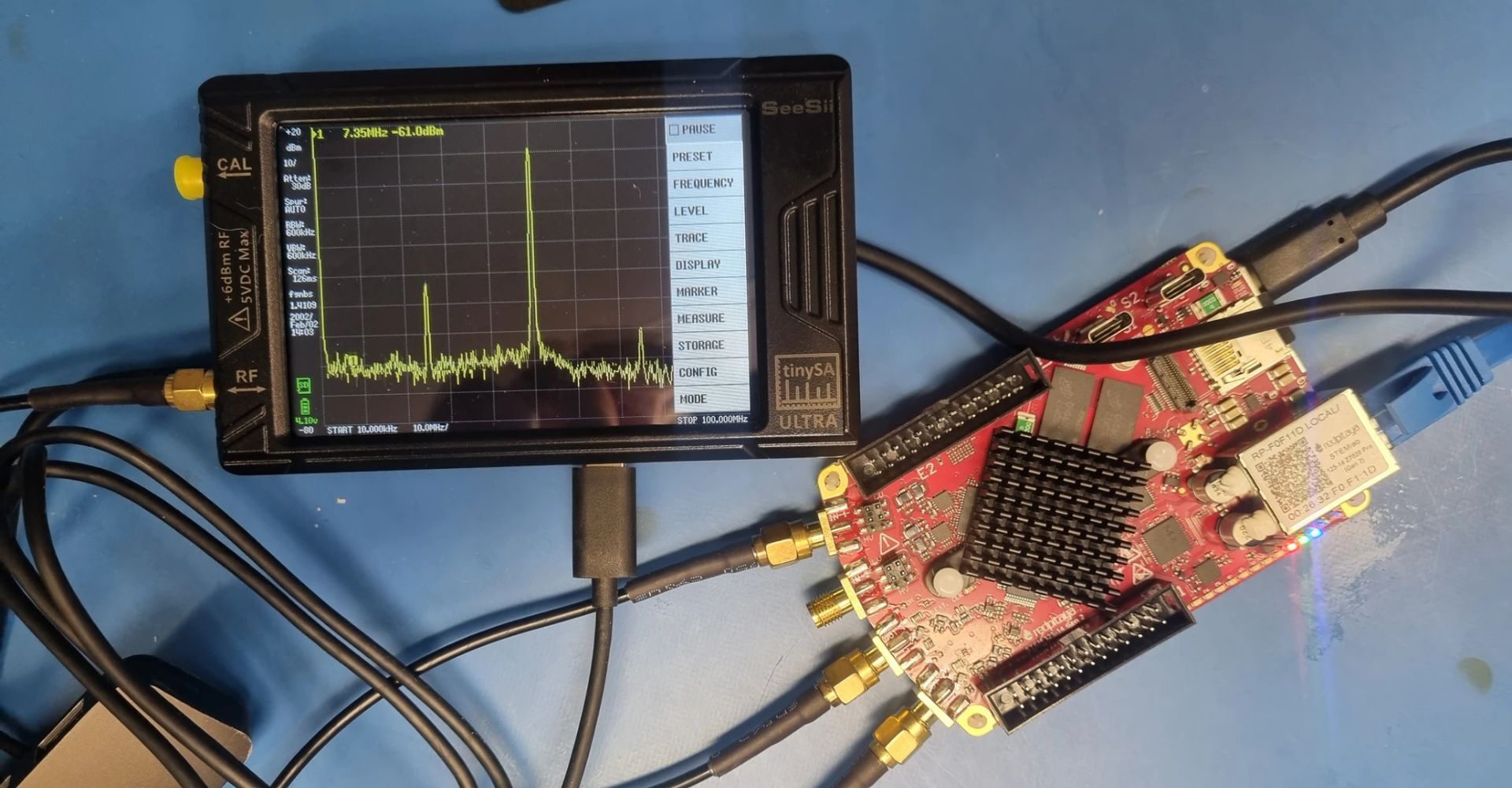

In his evaluation, Adam Taylor (MicroZed Chronicles) tested the Red Pitaya’s RF performance using a Tiny Spectrum Analyzer (TinySA). Testing focused on fundamentals and harmonics at 10 MHz, 20 MHz, and 50 MHz.

- DAC Performance: Output testing revealed expected harmonics due to the onboard low-pass filter (approx. 50 MHz cutoff), suggesting that users generating lower-frequency signals may require additional external filtering for higher spectral purity.

- ADC Characterization: The front-end low-pass filter impact was clearly visible when generating 60 MHz tones, demonstrating the hardware's roll-off characteristics at the edge of its sampling Nyquist limit.

Why This Matters for 2026

The shift toward Software-Defined Instrumentation is accelerating. The ability to take a design from Vitis Model Composer and deploy it directly onto the Red Pitaya's Zynq architecture enables engineers to build custom RF applications—like software-defined radios or quantum control systems—with significantly reduced development cycles.

Read the full original article on MicroZed Chronicles: RF Signal Processing with Red Pitaya

FAQ: RF Signal Processing with Red Pitaya

What is Vitis Model Composer?

It is a toolset for MATLAB/Simulink that allows engineers to design FPGA-ready DSP algorithms using blocks that automatically generate HLS or HDL code.

Can Red Pitaya be used with Python?

Yes. The Red Pitaya features a full Linux OS and a Python API, making it easy to control the ADCs and DACs for automated testing or data acquisition.

What is the sampling rate of the Red Pitaya STEMlab 125-14?

It samples at 125 MSPS, making it suitable for RF signals up to approximately 50–60 MHz.

About the Red Pitaya Team

The Red Pitaya Technical Editorial Team is a cross-functional group of technical communicators and product specialists. By synthesizing insights from our hardware developers and global research partners, we provide verified, high-value content that bridges the gap between open-source innovation and industrial-grade precision.

Our mission is to make advanced instrumentation accessible to engineers, researchers, and educators worldwide.

.png?width=767&name=blog%20featured%20image%20(10).png)