Remote FPGA Verification with Real Signals Using Red Pitaya Gen2

-

Posted by

Red Pitaya Technical Editorial Team

, April 8, 2026

Red Pitaya Technical Editorial Team

, April 8, 2026

Simulation catches logic errors. It does not tell you what happens when your design meets real analog signals, non-ideal ADC behavior, or noisy interfaces. That gap becomes critical as soon as your FPGA is part of a larger system.

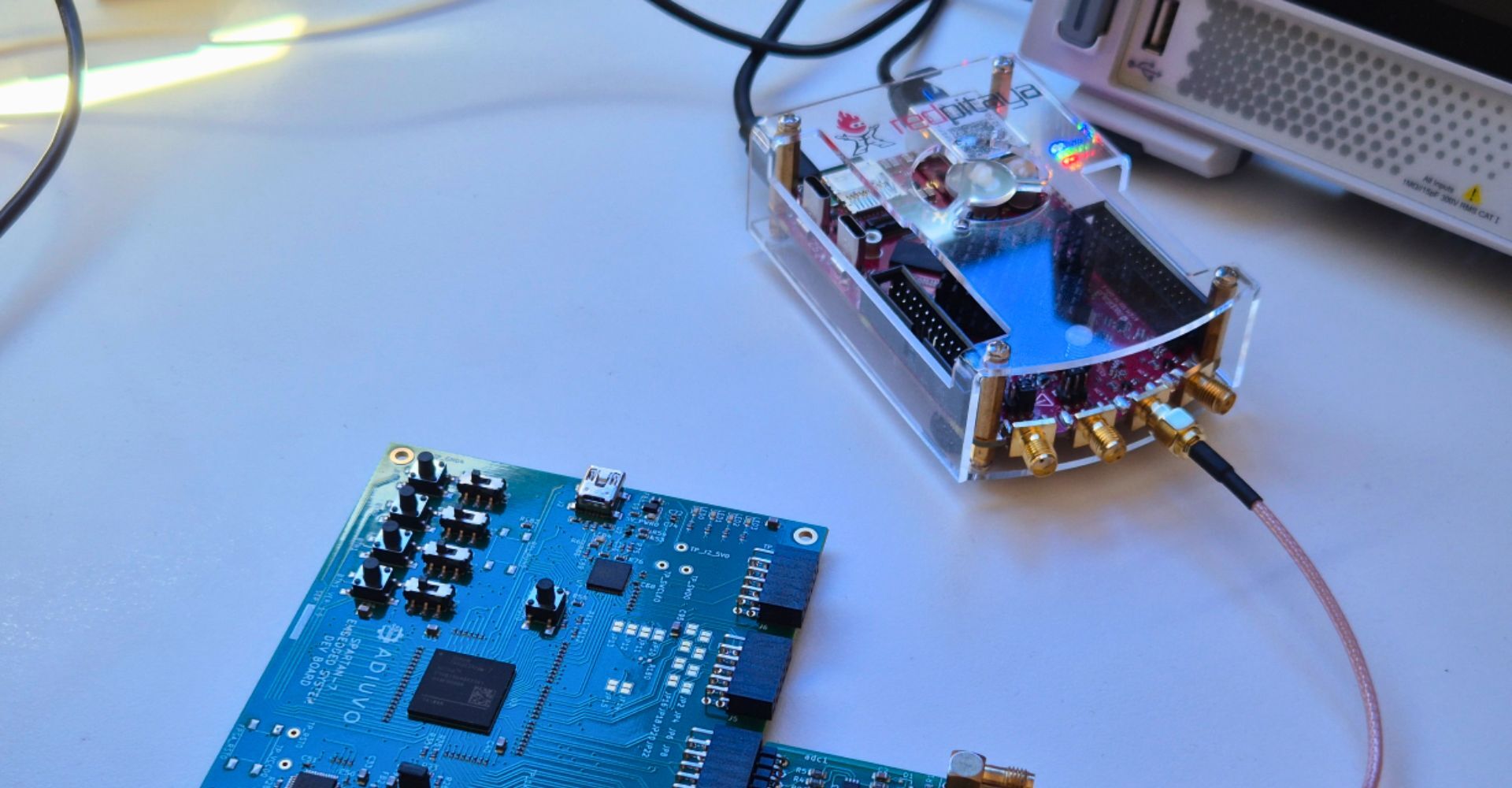

In a recent project by Pablo Trujillo Juan, this gap is addressed with a practical setup for remote, automated FPGA verification using real analog signals. The Red Pitaya STEMlab 125-14 Gen2 PRO acts as a programmable signal source, enabling analog-in-the-loop testing without requiring constant physical lab access.

From Simulation to Analog-in-the-Loop

A well-designed testbench validates functionality and timing. What it cannot capture are system-level effects—ADC offsets, SPI timing margins, coupling noise, or front-end nonlinearities.

This project extends verification into the physical domain by closing the loop:

- A Python script orchestrates the test

- Red Pitaya generates controlled analog stimuli via SCPI

- An external ADC digitizes the signal

- A Spartan-7 FPGA processes the data (Goertzel filter)

- Results are returned and evaluated automatically

Because both the instrument and FPGA are remotely controlled (Ethernet + UART), the entire workflow can run unattended.

Why Red Pitaya Matters Here

The key enabler is not just signal generation—it is programmable, network-accessible instrumentation.

Using SCPI over TCP, the system can:

- Generate precise sine tones across a defined sweep

- Update parameters dynamically during runtime

- Integrate directly into Python-based verification scripts

This effectively replaces bench equipment with a software-defined test node, suitable for automation and CI pipelines.

Verification Strategy

Instead of full spectral characterization, the test uses a targeted three-tone approach per frequency bin:

- A tone below the target frequency

- The target tone

- A tone above the target

This allows simultaneous validation of detection and rejection with minimal overhead. Results are evaluated against thresholds and exported as structured reports.

The DSP algorithm under test—a Goertzel filter—is configurable at runtime, enabling reuse of the same FPGA bitstream across multiple test conditions.

Practical Implications

This approach is particularly relevant when:

- FPGA designs interact with real analog front ends

- Hardware access is limited or distributed

- Repeatable validation is required across builds

It introduces a verification layer that sits between simulation and full system deployment—capturing failure modes that are otherwise difficult to reproduce.

Read the Full Technical Breakdown

This is a condensed overview. The full article includes:

- Verilog implementation details

- SPI and UART interfaces

- SCPI control examples

- Complete Python automation scripts

→ Remote FPGA verification of DSP algorithm using Red Pitaya Gen2 | controlpaths.com

FAQ

What is analog-in-the-loop verification?

It is a testing method where real analog signals are injected into a system to validate behavior across the full signal chain, not just the digital logic.

Why is simulation alone not sufficient?

Simulation cannot model real-world imperfections such as noise, ADC nonlinearities, timing jitter, or PCB-level effects.

What role does Red Pitaya play in this setup?

It functions as a remotely controlled signal generator, delivering precise, programmable analog inputs via SCPI over Ethernet.

Can this setup run fully remotely?

Yes. The Red Pitaya is controlled over TCP/IP, and the FPGA communicates via UART, allowing the entire test loop to run without physical access.

Is this approach limited to the Goertzel filter?

No. The same architecture can be used to validate any DSP or FPGA design that processes real-world signals.

Can this be integrated into CI/CD workflows?

Yes. The Python-based test runner produces machine-readable outputs and can be triggered automatically after FPGA builds.

About the Red Pitaya Team

The Red Pitaya Technical Editorial Team is a cross-functional group of technical communicators and product specialists. By synthesizing insights from our hardware developers and global research partners, we provide verified, high-value content that bridges the gap between open-source innovation and industrial-grade precision.

Our mission is to make advanced instrumentation accessible to engineers, researchers, and educators worldwide.

.png?width=767&name=blog%20featured%20image%20(10).png)