Evolving the Platform: Comparing the Original STEMlab 125-14 to Gen 2

-

Posted by

Red Pitaya Technical Editorial Team

, July 23, 2025

Red Pitaya Technical Editorial Team

, July 23, 2025

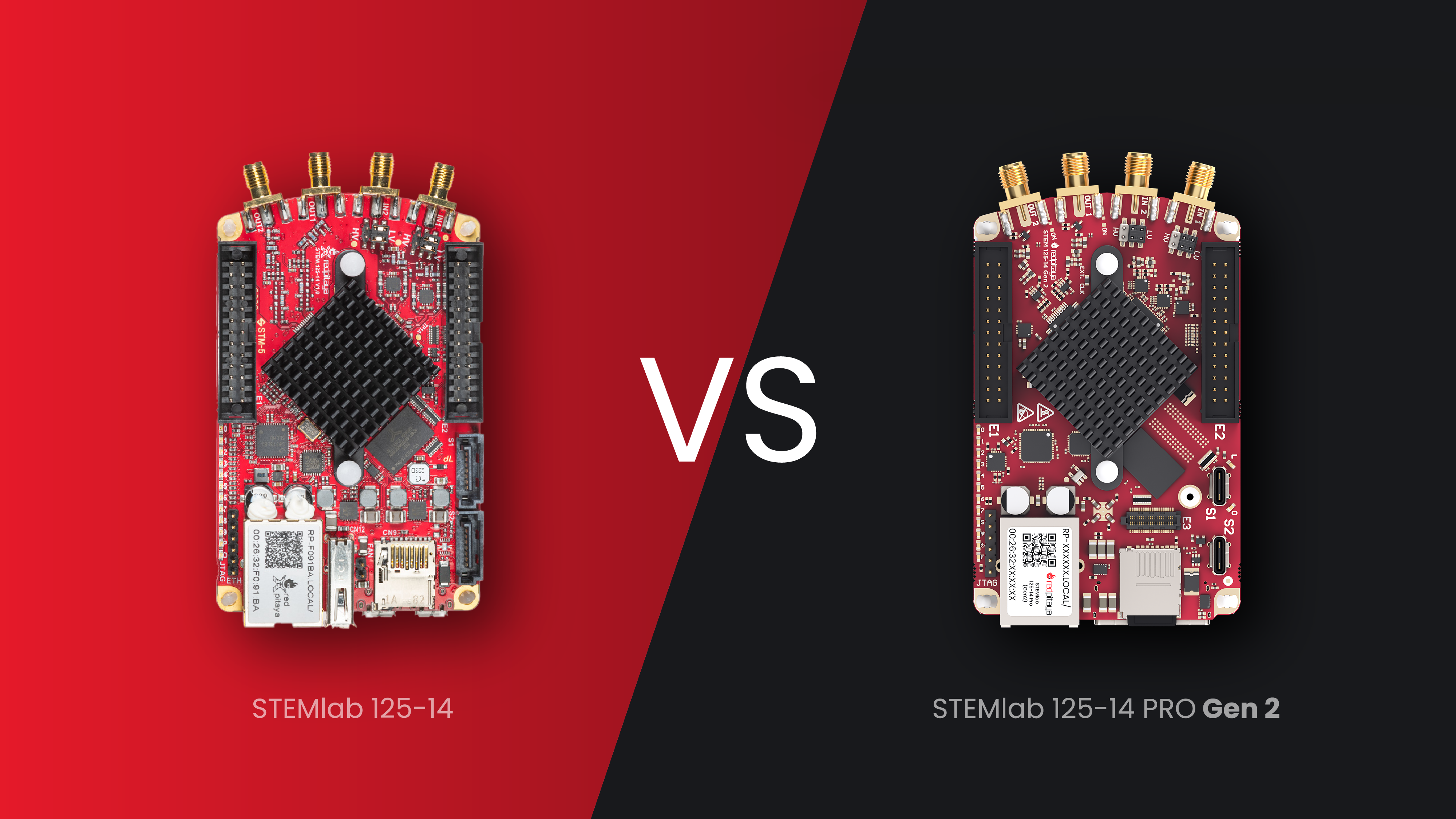

When we set out to develop Gen 2, our goal was simple: keep everything that made the STEMlab 125‑14 great—same board size, same connectors, full software and FPGA compatibility—while significantly improving performance and reliability for real-world engineering use.

The STEMlab 125‑14 Gen 2 series brings enhanced performance to the original STEMlab platform, featuring a revamped analog front end, modern USB‑C connectivity, and firmware-selectable QSPI/eMMC boot options on Pro models. Available in three versions, the Gen 2 line supports use cases ranging from teaching labs and makerspaces to synchronized industrial test benches and real-time, high-channel-count DSP. An optional QSPI/eMMC Boot Module adds safe-shutdown sequencing, and sixteen fast GPIOs are exposed on the E3 connector—no module required—all controlled via open-source firmware.

Gen 2 Design Goals and Key Enhancements

Enhanced Analog Performance

SFDR Improvement

Increased from 40 dB to 50 dB at 10 MHz / 10 dBm, delivering significantly cleaner spectra.

Crosstalk Reduction

Reduced crosstalk from 55 dB to 70 dB up to 30 MHz, minimizing measurement interference.

Noise Floor & Ranges

Lowered the overall noise floor while preserving the familiar ±1 V full-scale range into 50 Ω and ±2 V into high-impedance mode—ensuring compatibility with existing probes and accessories.

Flexible Boot & Robust Power Management

E3 Connector

Exposes QSPI flash, eMMC storage, and watchdog-under-clock interfaces for firmware-controlled boot selection—no manual media swaps required.

Safe Shutdown

An onboard STM32 microcontroller manages single-button on/off control, a hardware watchdog, and orderly shutdown to protect filesystems in the event of power interruptions.

Scalable FPGA & Memory Configurations

Gen 2: Xilinx Zynq 7010 with 512 MB DDR3, suitable for general-purpose signal generation and acquisition.

PRO Gen 2: Same SoC and memory, with the addition of the E3 boot/I/O extension for industrial applications.

PRO Z7020 Gen 2: Xilinx Zynq 7020 with 1 GB DDR3—offering roughly three times the FPGA fabric and twice the RAM—geared toward complex, real-time DSP and analytics workloads.

Modern Connectivity & Precise Synchronization

USB‑C Power & Data

Includes two USB‑C data ports plus a dedicated USB‑C power port delivering up to 5 V / 3 A, simplifying cabling and supporting modern USB‑C power supplies.

Clock Selection

External reference via SMA or internal 125 MHz oscillator—selection managed through pins on the E2 connector.

Multi‑Unit Sync

Built-in header and USB‑C daisy-chaining capability support synchronized operation, ideal for phased-array and MIMO setups.

QSPI eMMC Boot Module Overview

The optional Boot Module Gen 2 plugs into the PRO boards’ E3 connector to provide:

Power Sequencing: STM32‑driven single‑button ON/OFF, hardware watchdog, and safe shutdown to prevent storage corruption.

Boot Media Flexibility: Firmware‑selectable boot from microSD, QSPI flash, or high‑speed eMMC for faster, more reliable startups.

Open‑Source Firmware: Preloaded Arduino IDE C++ code, fully modifiable for bespoke power and boot logic.Gen 2 extends the STEMlab 125‑14 platform into a flexible, software-defined instrumentation system by combining enhanced analog fidelity, modern USB‑C connectivity, flexible boot and power sequencing, scalable FPGA resources, and precise synchronization—all within a backward-compatible package. The optional QSPI/eMMC Boot Module adds safe-shutdown sequencing under open-source firmware control, enabling engineers to confidently address applications across education, research, and industry—without compromise.

About the Red Pitaya Team

The Red Pitaya Technical Editorial Team is a cross-functional group of technical communicators and product specialists. By synthesizing insights from our hardware developers and global research partners, we provide verified, high-value content that bridges the gap between open-source innovation and industrial-grade precision.

Our mission is to make advanced instrumentation accessible to engineers, researchers, and educators worldwide.

.png?width=767&name=blog%20featured%20image%20(10).png)