Phase Noise and Frequency Stability of the Red Pitaya Internal PLL

-

Posted by

Red Pitaya Technical Editorial Team

, February 29, 2024

Red Pitaya Technical Editorial Team

, February 29, 2024

In the fast-paced world of technology, precision in time and frequency measurements is critical for advancements and efficiency. While Red Pitaya integrates key components for streamlined operations, achieving measurement precision requires synchronization to a common oscillator. However, the platform's onboard oscillator may lack the requisite accuracy for certain tasks, necessitating an external reference. Leveraging the FPGA's internal Phase Locked Loop (PLL) offers a cost-effective way to achieve this, despite limited documentation on its suitability for low phase noise applications. This study focuses on evaluating the PLL's stability within Red Pitaya, analyzing its phase noise in relation to the external reference power and frequency to predict noise levels across diverse operational conditions.

Characterization method

Examining the intricacies of the Phase Locked Loop (PLL) within the Red Pitaya system reveals a sophisticated mechanism critical for achieving precise time and frequency measurements. The PLL, essential for synchronizing the system's frequency with an external reference, operates through a Voltage Controlled Oscillator (VCO) that adjusts its frequency based on the phase and frequency differences that are detected. This setup allows for a range of output signals, each customizable through user-defined parameters.

At the heart of the PLL's efficiency is its ability to minimize phase noise, represented in the frequency domain through its Power Spectral Density (PSD). This method of characterizing phase noise as a function of external reference power and frequency is pivotal for optimizing the PLL's performance under various conditions. Notably, the PLL's ability to handle phase noise is crucial for maintaining the stability and accuracy of the Red Pitaya's measurements.

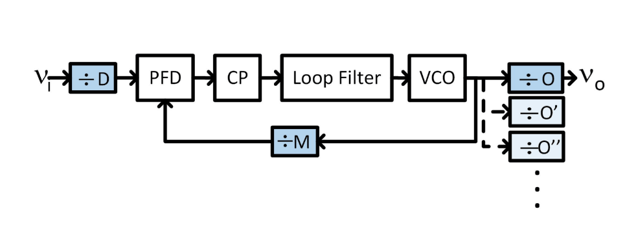

Fig. 1: PLL block diagram. Scheme of Xilinx FPGA Internal

PLL.

Two significant sources of noise affecting the PLL are voltage noise and time noise, each with its own impact on the system's performance. Voltage noise stems from the input threshold, while time noise arises from the delay fluctuations in the PLL's logical gates. Understanding and mitigating these types of noise are essential for enhancing the PLL's output stability.

The process for measuring this phase noise involves a sophisticated test bench setup that includes a phasemeter capable of distinguishing the PLL's noise from other sources. This allows for the precise assessment of the PLL's performance and the identification of optimal operating conditions to minimize noise.

The PLL's characterization method not only sheds light on the technical challenges of minimizing phase noise but also highlights the Red Pitaya's versatility and capability in addressing complex metrological needs. Through detailed analysis and experimentation, this method contributes significantly to the field of time and frequency metrology, offering a pathway to improved precision and reliability in measurements.

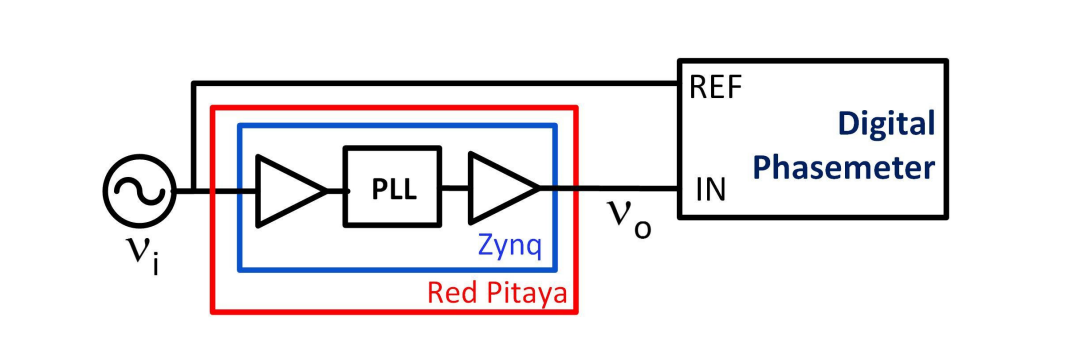

Fig. 2: Test bench for measuring the residual phase noise of the

PLL.

Results

The research explores the impact of high-quality external references on the frequency stability of the Red Pitaya's Phase Locked Loop (PLL), which is vital for providing a precise timebase for digital systems, including Field-Programmable Gate Arrays (FPGAs), Analog-to-Digital Converters (ADCs), and Digital-to-Analog Converters (DACs). The experiments focused on the PLL output, set at 125 MHz, the system clock of the Red Pitaya, to analyze the phase noise with a keen interest in the flicker noise region, essential for the accuracy of time and frequency measurements.

The researchers observed a dramatic improvement in the PLL's performance when it was synchronized with external references at 10 MHz and 100 MHz. Specifically, the phase noise at 1 Hz saw a significant reduction, and the Allan deviation—a measure of stability over time—showed substantial improvements. This underscored the critical role of external references in enhancing frequency stability and achieving high precision in measurements.

Further exploration involved varying the input power and carrier frequency to understand their influence on the PLL's behavior. At 10 MHz, it was found that the flicker phase noise decreased as the input power increased, indicating that input stage noise was a limiting factor. However, at 100 MHz the phase noise remained consistent across different input power levels, suggesting that at these higher frequencies the system's time noise, rather than voltage noise, was more influential.

These findings highlight the adaptability and effectiveness of Red Pitaya's PLL in time and frequency metrology, especially when paired with high-quality external references. The detailed analysis provides valuable insights for leveraging this technology in precision instruments, marking a significant advancement in the field of time and frequency measurement.

Conclusion

In conclusion, the internal Phase Locked Loop (PLL) of the Red Pitaya platform was examined for its relevance in time and frequency metrology. The study effectively distinguished and quantified two main types of noise, n(t) and x(t), by varying the input power and carrier frequency, finding specific noise levels for each. It was demonstrated that optimal phase noise performance is achieved when the PLL reference's slew rate surpasses 156 V/μs, minimizing the impact of the input-stage threshold relative to the time fluctuations in the PLL path.

This methodology is not exclusive to Red Pitaya's PLL and is also applicable to other PLLs, like those in the Cyclone III, showcasing similar time noise but halved voltage noise in the Cyclone III compared to the Red Pitaya.

The study underscored the internal PLL's flexibility and its suitability for a wide range of time and frequency applications, thanks to its frequency stability of 1.2 × 10^-12 at 1 s for a 10 MHz reference. This level of stability makes it a viable option for most applications in this field, marking a significant step forward in the use of the Red Pitaya for precise time and frequency measurements.

Read more about this project here.

About the Red Pitaya Team

The Red Pitaya Technical Editorial Team is a cross-functional group of technical communicators and product specialists. By synthesizing insights from our hardware developers and global research partners, we provide verified, high-value content that bridges the gap between open-source innovation and industrial-grade precision.

Our mission is to make advanced instrumentation accessible to engineers, researchers, and educators worldwide.

.png?width=767&name=blog%20featured%20image%20(10).png)